Using ghdl instead of Quartus II

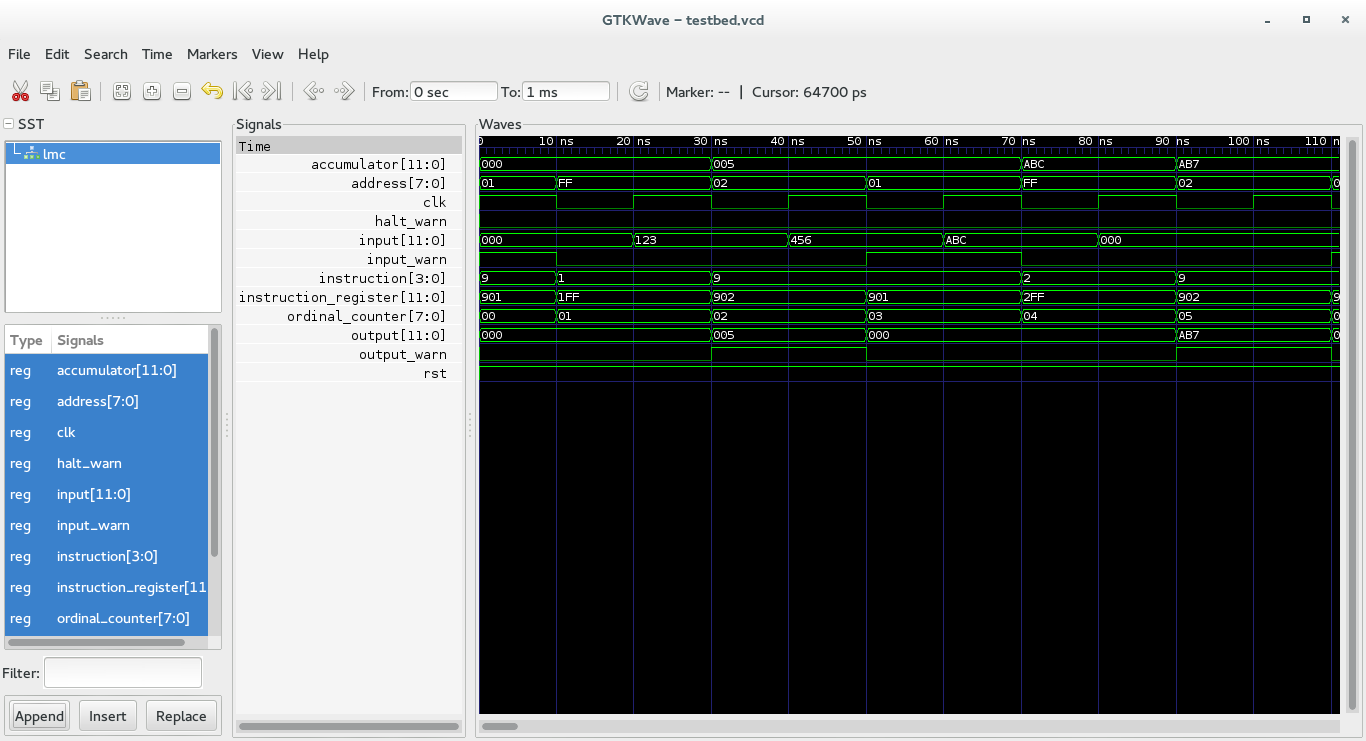

ghdl is a great tool to prototype hardware quickly. It can be combined with gtkwave to analyze signals.

I did hardware design last semester and this is a bit tough for my mind right now, but I think it could help others out having a hard time with Quartus II. This post explain how to replace Quartus in the process of developing the device …

First of all, you need ghdl and gtkwave installed on your workstation.

yum install ghdl gtkwaveThen you can create a sample project or clone one I did last semester.

git clone https://github.com/arteymix/ghdl-lmc.gitA project usually consist of entities and testbeds on these entities. A testbed applies entries on an entity and make assertions on outputs.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

library work;

entity testbed is

end entity;

architecture testbed of testbed is

type inputs_t is array(0 to 255) of signed(11 downto 0);

constant inputs: inputs_t := (

0 => x"000",

1 => x"123",

2 => x"456",

3 => x"ABC",

others => x"000"

);

signal cycle: natural := 0;

signal clk: std_logic := '1';

signal input: signed(11 downto 0) := inputs(cycle);

begin

input <= inputs(cycle mod 256);

lmc: entity work.lmc port map(clk, '1', input);

process is

begin

while TRUE loop

clk <= '1';

wait for 10 ns;

clk <= '0';

wait for 10 ns;

cycle <= cycle + 1;

end loop;

end process;

end architecture;

ghdl can generate a Makefile for a specified unit

ghdl --gen-makefile testbedghdl can analyze, elaborate or run a simulation. The analyze part is essential

as it will generate object files for each entities. Then you can link all those

into a single executable. This is automated by the make command.

makeOnce you have a correct result, you may run it and capture signals

./testbed --vcd=testbed.vcdgtkwave is a tool designed to analyze signals, specifically the generated vcd file.

gtkwave testbed.vcdIn gtkwave, you have to select the device in SST section and append the signals on your workarea. You may then zoom it and out to see the actual waves.

I really hope this will help you out! I did enjoy VHDL and I really liked learning Ada-like syntax.